Difference between revisions of "Interfacing with a Photodiode Array"

From Mech

Jump to navigationJump to search| Line 1: | Line 1: | ||

| ⚫ | |||

| ⚫ | |||

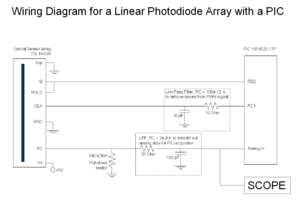

One way to interface with the TAOS Photodiode Linear Sensor Array (TSL1406R) is provides an analog output for each of the photodiodes in the array. During the integration time, a capacitor is charged by the photodiode. When the HOLD goes high, each of the charges accumulated during the integration time is simultaneously passed to its holding capacitor. The analog voltages on each holding capacitor are read then read one-by-one at the clock speed. We are using the PWM function of the PIC to act as the CLK signal. |

One way to interface with the TAOS Photodiode Linear Sensor Array (TSL1406R) is provides an analog output for each of the photodiodes in the array. During the integration time, a capacitor is charged by the photodiode. When the HOLD goes high, each of the charges accumulated during the integration time is simultaneously passed to its holding capacitor. The analog voltages on each holding capacitor are read then read one-by-one at the clock speed. We are using the PWM function of the PIC to act as the CLK signal. |

||

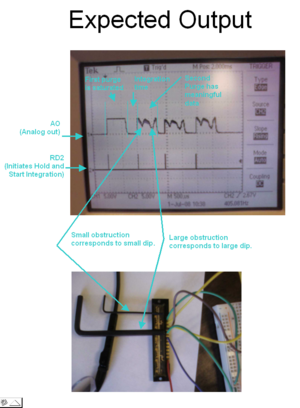

In this interfacing structure, the data is clocked out so quickly that it is impossible to read every analog level. To remedy this, we low pass filter the analog output and read in analog data as quickly as possible. |

In this interfacing structure, the data is clocked out so quickly that it is impossible to read every analog level. To remedy this, we low pass filter the analog output and read in analog data as quickly as possible. |

||

| ⚫ | |||

| ⚫ | |||

Revision as of 13:38, 2 July 2008

One way to interface with the TAOS Photodiode Linear Sensor Array (TSL1406R) is provides an analog output for each of the photodiodes in the array. During the integration time, a capacitor is charged by the photodiode. When the HOLD goes high, each of the charges accumulated during the integration time is simultaneously passed to its holding capacitor. The analog voltages on each holding capacitor are read then read one-by-one at the clock speed. We are using the PWM function of the PIC to act as the CLK signal.

In this interfacing structure, the data is clocked out so quickly that it is impossible to read every analog level. To remedy this, we low pass filter the analog output and read in analog data as quickly as possible.